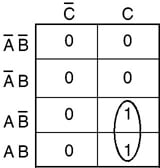

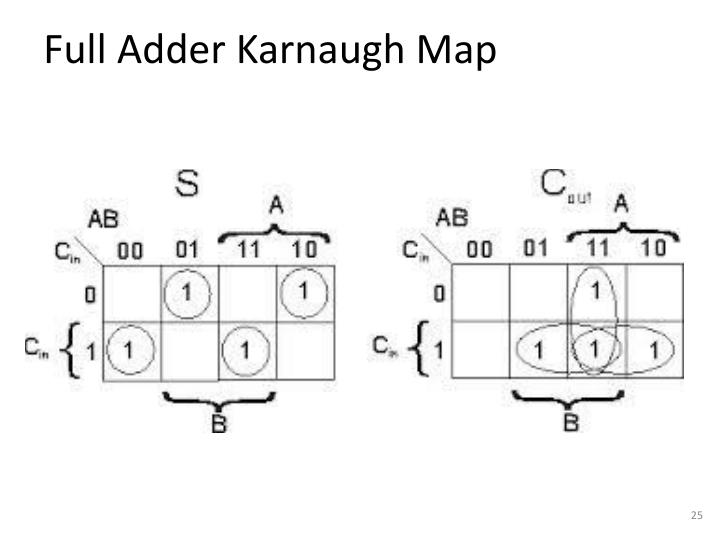

K Map Of Full Adder

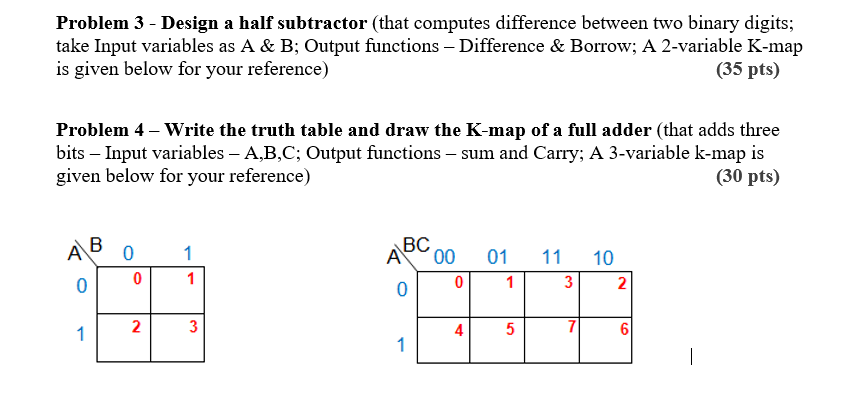

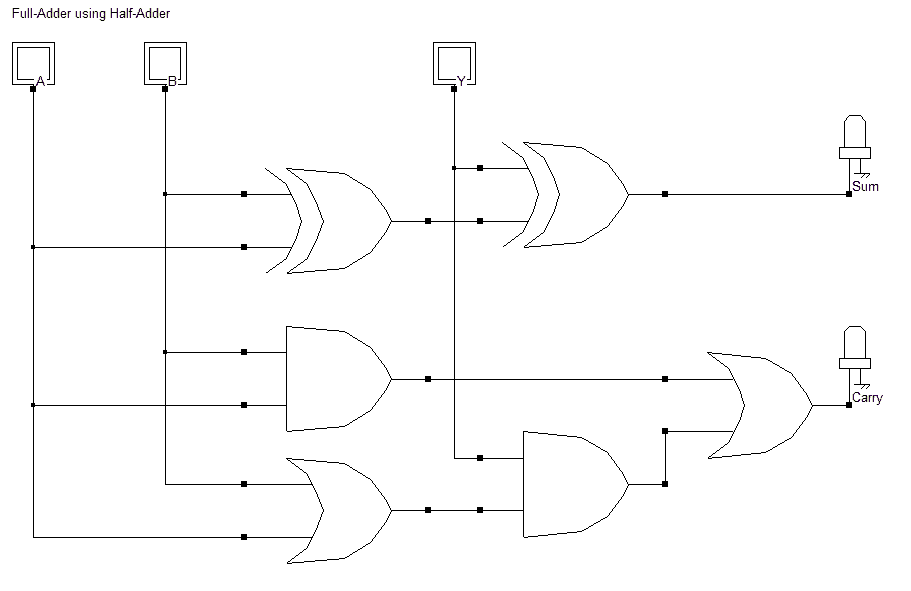

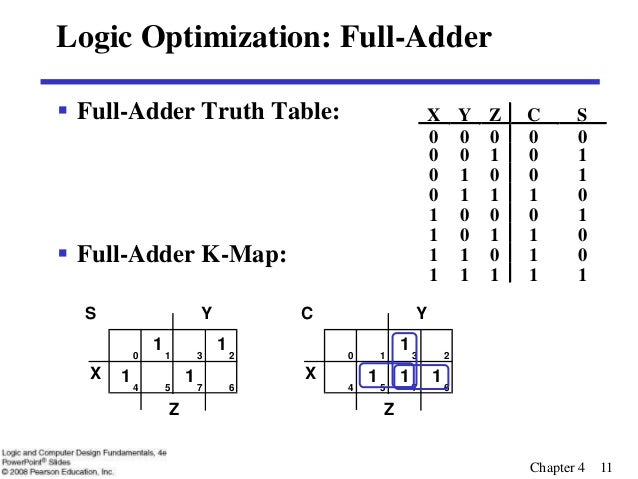

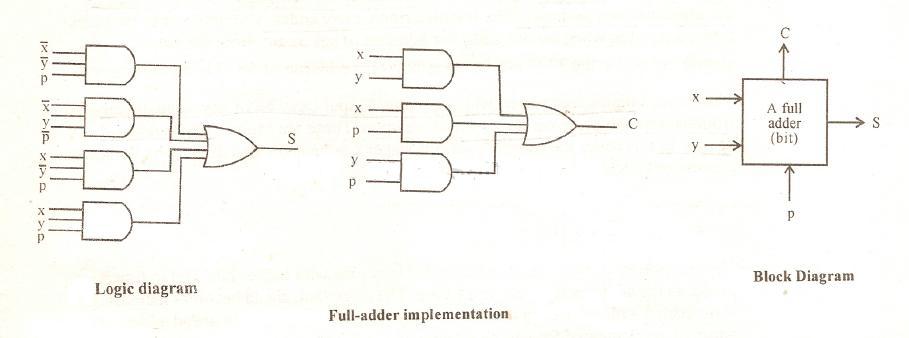

K Map Of Full Adder. Full addition requires carry-in and carry-out bits. Using K-map in Full Adder Circuit. This can be derived by the use. It is used for the purpose of adding two single bit numbers with a carry.. Here are a number of highest rated Full Adder K Map pictures on internet. K Map Of Full Adder

K Map Of Full Adder Its submitted by handing out in the best field. This can be derived by the use. The above block diagram describes the construction of the Full adder circuit.

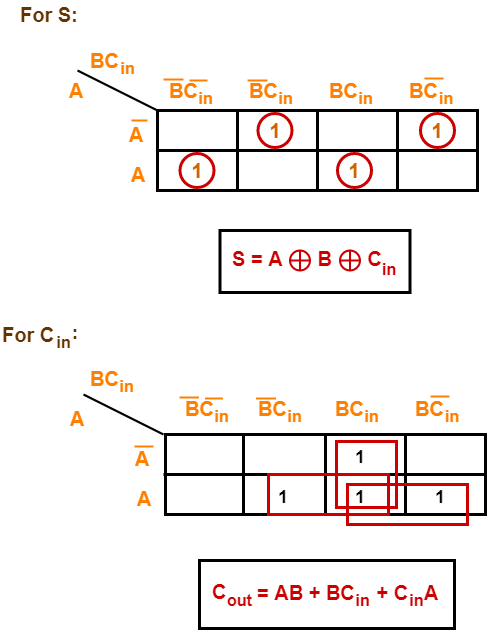

Hence, from K-maps, Binary Parallel Adder.

Simply, a circuit in which different types of logic gates are combined.

K Map Of Full Adder ADDER : IN ELECTRONICS AN ADDER IS DIGITAL CIRCUIT THAT PERFORM ADDITION Half Adder and Full Adder using K-Map. The output carry is designated as C-OUT and the normal output is designated as S which is SUM. Draw K

-maps using the above truth table and determine the simplified Boolean expressions- Also Read.